# **Universidade do Minho**

Escola de Engenharia

João Pedro Marques da Silva Martins

**Formal Verification of Ada Programs: An Approach Based on Model Checking**

João Martins on Model Checking

## **Universidade do Minho** Escola de Engenharia

João Pedro Marques da Silva Martins

# Formal Verification of Ada Programs: An Approach Based on Model Checking

Tese de Mestrado Mestrado em Informática

Trabalho efectuado sob a orientação do **Professor Doutor Jorge Sousa Pinto**

The EVOLVE (Evolutionary Validation, Verification and Certification) is a collaboration project, developed by the consortium leader Critical Software SA and the University of Minho. The consortium's major intention is to develop the sustained development of innovative know-how throughout the cooperation between R&D institutions and companies appointed for embedded systems. This is co-funded by EUR 258.335,56 (two hundred and fifty eight thousand, three hundred and thirty five euros and fifty six cents) by QREN, under the Operational Programme for Competitiveness Factors and contracted with ADI through the Contrato de Concessão Incentivos Financeiros n. 2008/001621 with the total amount of investment of EUR 404.131,97 (four hundred and four thousand, one hundred and thirty one euros and ninety seven cents) with the execution period planned for between the 01-06-2008 e 31-09-2011. This work was partially supported by the EVOLVE Project.

# Acknowledgements

I would like first to thank my family, you are my great inspiration. I dedicate this thesis to my mother, my father, Hugo and Lili for their enthusiasm and expectations from me.

I also would like to thank my friends from Cabeceiras de Basto and Braga for providing me relaxing and funny moments, which gave me the strength i needed when things were not going well.

Lastly, a special thank to my advisor from Critical Software José Miguel Faria and to my advisor in University of Minho prof. Jorge Sousa Pinto. Thank you for all the guidance and help provided, but thank you especially for the support and motivation you gave me.

#### Resumo

O rápido crescimento da complexidade dos sistemas de software exige, agora mais do que nunca, uma validação rigorosa dos mesmos por forma a manter ou até mesmo aumentar a confiança nestes sistemas. Em particular nos sistemas críticos, onde as falhas podem ter consequências catastróficas podendo até incluir a perca de várias vidas humanas, é de extrema importâcia o desenvolvimento de técnicas capazes de garantir altos níveis de confiança para estes sistemas.

Nesta tese é proposta a utilização de uma técnica formal para a verificação de programas Ada, que pretende aumentar a confiança em sistemas cuja implementação seja realizada nesta linguagem de programação. Mais precisamente, pretende-se a aplicação da técnica de verificação de modelos para a análise do código fonte de programas concorrentes Ada, com especial foco para o domínio dos sistemas críticos.

A vericação de modelos é uma técnica bem sucedida no que diz respeito à garantia de um aumento de fiabilidade destes sistemas. No entanto, a aplicação desta técnica a sistemas de software enfrenta ainda vários obstáculos, e as ferramentas e técnicas para ajudar a ultrapassar estes obstáculos estão ainda a ser desenvolvidas. A ferramenta desenvolvida no contexto desta tese (ATOS) visa responder a problemas como (i) a construção de modelos a partir de programas e (ii) a especificação de propriedades para estes modelos de acordo com as pretendidas para os programas.

A construção manual de modelos que simulam o comportamento de programas é um processo complexo, temporalmente dispendioso, e sujeito a falhas devido à complexidade destes sistemas. De forma a ultrapassar este problema o ATOS propõe a extracção automática de modelos a partir de programas Ada. Por outro lado, o mapeamento das propriedades desejadas dos programas em propriedades dos modelos pode ser uma tarefa com um grau de complexidade elevado, pois requer entre outros a utilização de um formalismo lógico ao qual a maioria dos programadores não está acostumado. O ATOS ajuda no mapeamento destas propriedades, oferecendo vários mecanismos de suporte à sua especificação.

Palavras-chaves: Ada, Extração de Modelos, Lógica Temporal, Métodos Formais, Sistemas Críticos, SPIN, Verificação de Programas, Verificação Formal, Vericação de Modelos, Vericação de Modelos de Software.

#### **Abstract**

The rapid growth of the complexity of software systems demands, now more than ever, a rigorous validation of these systems in order to maintain or even increase their reliability. In particular in high-integrity systems, where failures may have catastrophic consequences which may even include the lost of human lives, the development of verification techniques capable of ensuring high degrees of confidence is seen as extremely important.

In this thesis the use of a formal technique for the verification of Ada programs is proposed, which aims to increase the reliability of systems whose implementation is based on this programming language. More precisely, we target the application of the model checking technique to the verification of source code of concurrent Ada programs, with a special focus on the critical systems domain.

Model checking is a well-succeeded technique for providing increased levels of assurance regarding system correctness. However, its application to software systems still faces several obstacles, and the necessary tools and techniques to help in the overcoming of these problems are still being developed. The tool presented in this thesis (ATOS) addresses the problems of (i) constructing models from programs and (ii) specifying properties for models corresponding to the ones desired for programs.

The manual construction of models that simulate the behavior of programs is a time-costly, complex and error-prone process, due to the complexity of these systems. In order to overcome this problem, ATOS proposes the automatic extraction of models from Ada programs. On the other hand, the mapping of the desired properties from programs to models can be a task of high complexity, because it requires among others that they are expressed in a logical formalism that most programmers are not acquainted with. ATOS helps in this mapping task by providing several mechanisms aiming to support the specification of properties.

Keywords: Ada, Critical Systems, Formal Methods, Formal Verification, Model Checking, Model Extraction, Software Verification, Software Model Checking, SPIN, Temporal Logic.

# Contents

| 1. | Intro | oduction                                                   | 1  |

|----|-------|------------------------------------------------------------|----|

|    | 1.1.  | Formal Verification of Software Systems                    | 1  |

|    | 1.2.  | Verification of Critical Systems in the Industrial Context | 3  |

|    | 1.3.  | Formal Verification of Ada Programs                        | 5  |

|    | 1.4.  | Verification of Software Systems using Model Checking      | 6  |

|    | 1.5.  | A Formal Approach to the Verification of Ada Programs      | 8  |

|    | 1.6.  | Contributions and Document Outline                         | 9  |

| 2. | Mod   | lel Checking - Approaches, Theories and Tools              | 11 |

|    | 2.1.  | Mathematical models                                        | 12 |

|    |       | 2.1.1. Automata                                            | 12 |

|    |       | 2.1.2. Petri Nets                                          | 12 |

|    | 2.2.  | Temporal Logic                                             | 13 |

|    |       | 2.2.1. LTL                                                 | 13 |

|    |       | 2.2.2. CTL                                                 | 14 |

|    |       | 2.2.3. CTL*                                                | 15 |

|    |       | 2.2.4. TCTL                                                | 15 |

|    | 2.3.  | Model Checking - Tools                                     | 16 |

|    |       | 2.3.1. SPIN                                                | 16 |

|    |       | 2.3.2. Uppaal                                              | 17 |

|    |       | 2.3.3. NuSMV                                               | 17 |

|    | 2.4.  | Software Model Checking - Tools                            | 18 |

|    |       | 2.4.1. Quasar                                              | 19 |

|    |       | 2.4.2. BLAST                                               | 21 |

|    |       | 2.4.3. Ada Translating Toolset                             | 22 |

|    |       | 2.4.4. Bandera                                             | 23 |

| 3. | An (  | Overview of ATOS                                           | 25 |

|    | 3.1.  | ASIS                                                       | 26 |

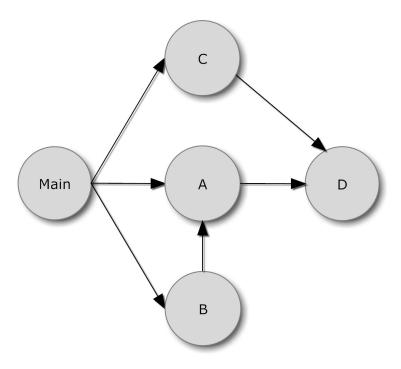

|    | 3.2.  | How To Compile from Main?                                  | 27 |

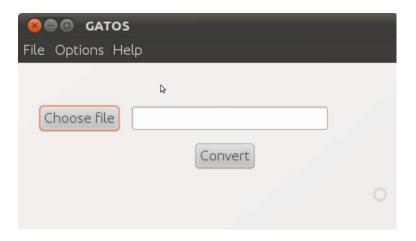

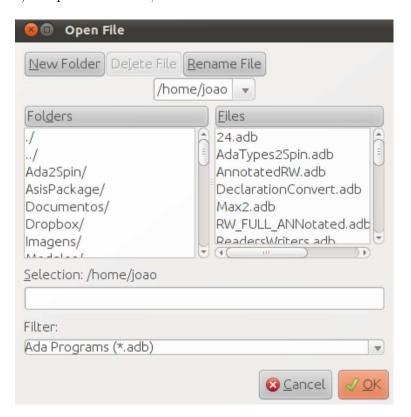

|    | 3 3   | GATOS - a graphical user interface for ATOS                | 29 |

| 4. | Mod  | lel Extraction                                     | 31             |

|----|------|----------------------------------------------------|----------------|

|    | 4.1. | Encapsulation                                      | 32             |

|    | 4.2. | Types                                              | 33             |

|    | 4.3. | Variables                                          | 38             |

|    | 4.4. | Subprograms                                        | 42             |

|    |      | 4.4.1. Procedures                                  | 43             |

|    |      | 4.4.2. Functions                                   | 45             |

|    | 4.5. | Packages                                           | 46             |

|    | 4.6. | Tasks                                              | 48             |

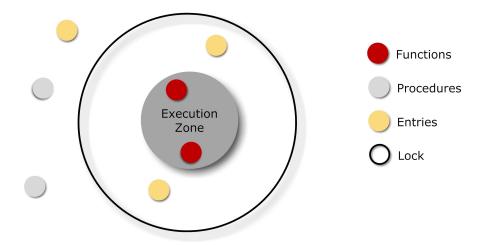

|    | 4.7. | Protected Objects                                  | 50             |

|    | 4.8. | Expressions                                        | 56             |

|    | 4.9. | Statements                                         | 59             |

|    | 4.10 | Main Program                                       | 39             |

| _  | Dua  | - Consideration                                    | 70             |

| Э. | -    | Derty Specification Inferred Properties            | 70<br>71       |

|    | 9.1. | •                                                  |                |

|    |      | 5.1.1. Range Checking                              |                |

|    | 5.2. |                                                    |                |

|    | ე.∠. | Annotations                                        |                |

|    |      | 5.2.1. Temporal properties                         | 12<br>74       |

|    |      | ,                                                  |                |

|    |      |                                                    | 76<br>76       |

|    | ۲ ،  | 5.2.4. Invariants                                  |                |

|    | 5.3. | Special Labels                                     | 1 1            |

| 6. | Ехр  | erimental Validation                               | 79             |

|    | 6.1. | Readers-Writers                                    | 79             |

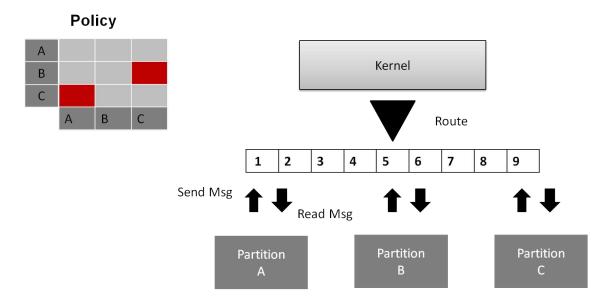

|    | 6.2. | Separation Kernel                                  | 34             |

|    | 6.3. | An overview of the experimental validation process | <del>)</del> 6 |

| _  | _    |                                                    |                |

| 1. |      |                                                    | 98<br>30       |

|    |      | Conclusions                                        |                |

|    | 7.2. | Limitations and Future Work                        | JU             |

| Α. | Prod | ducers-Consumers 10                                | 8(             |

|    | A.1. | Ada Program                                        | )8             |

|    |      | PROMELA Model                                      |                |

| _  |      |                                                    |                |

| В. | •    |                                                    | 15             |

|    | КI   | Ada Program                                        | 15             |

| B.2. PROMELA Model | 4 |

|--------------------|---|

|--------------------|---|

# List of Acronyms

**ANTLR** Another Tool for Language Recognition

**ASIS** Ada Semantic Interface Specifications

**AST** Abstract Syntax Tree

ATOS Ada Translation to Spin

**ATP** Automated Theorem Provers

**ASIL** Automotive Safety Integrity Levels

**BDD** Binary Decision Diagram

**BIR** Bandera Intermediate Representation

**BLAST** Berkeley Lazy Abstraction Software Verification Tool

**BSL** Bandera Specification Language

CC Common Criteria

CFA Control Flow Automata

$\textbf{CFG} \ \operatorname{Control} \ \operatorname{Flow} \ \operatorname{Graph}$

**CIL** C Intermediate Language

**CPN** Colored Petri Nets

CNES Centre National d'Etudes Spatiales

CTL Computation Tree Logic

**DAG** Direct Acyclic Graph

**DAL** Design Assurance Level

**DbC** Design by Contract

**DFA** Deterministic Finite Automata

**DFD** Data Flow Diagram

**EAL** Evaluation Assurance Level

**ESA** European Spatial Agency

**EVOLVE** Evolutionary Validation, Verification and Certification

**GB** Gigabyte

**GPS** Gnat Programming Studio

**GSW** Galileo Software Standard

**GUI** Graphical User Interface

**HELENA** High Level Net Analyzer

IDE Integrated Development Environment

IEC International Electrotechnical Commission

**ISO** International Organization for Standardization

JML Java Modeling Language

JPF Java Path Finder

LOC Lines Of Code

LTL Linear Temporal Logic

MB Megabyte

MILS Multiple Independent Levels of Security

MMR MILS Message Router

NFA Non-Deterministic Finite Automata

**NuSMV** New Symbolic Model Verifier

PROMELA Process or Protocol Meta Language

PIFP Partition Information Flow Policy

**RAM** Random Access Memory

**SEDL** S-Expression Design Language

**SIL** Safety Integrity Levels

**SMV** Symbolic Model Verifier

**SPARK** Spade Ada (?) Kernel

$\textbf{SPIN} \ \ \text{Simple PROMELA Interpreter}$

**SRS** Software Requirements Specification

TCTL Timed Computation Tree Logic

# List of Figures

| 1.1. | Formal methods effect on projects: time, cost and quality | 3  |

|------|-----------------------------------------------------------|----|

| 2.1. | The LTL view of time                                      | 14 |

| 2.2. | The CTL view of time                                      | 14 |

| 2.3. | CTL* expressive power                                     | 15 |

| 2.4. | The first phase of Quasar translation process             | 20 |

| 2.5. | The second phase of Quasar translation process            | 21 |

| 2.6. | The translation of program Max done by Blast              | 22 |

| 2.7. | The Ada Translating Toolset approach                      | 23 |

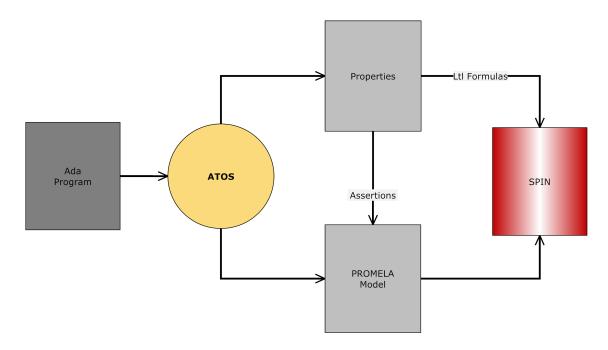

| 3.1. | ATOS process                                              | 26 |

| 3.2. |                                                           |    |

| 3.3. | GATOS main window                                         |    |

| 3.4. | The file selector of GATOS                                | 30 |

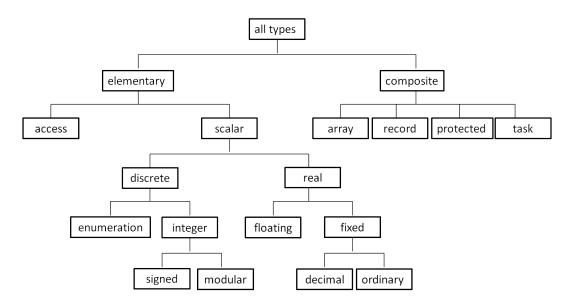

| 4.1. | Ada type Hierarchy                                        | 34 |

| 4.2. | Graphical representation of a protected object            | 51 |

| 6.1. | The MMR system                                            | 86 |

# List of Tables

| 1.1. | The standards generic table to assign the safety level of a system | 4  |

|------|--------------------------------------------------------------------|----|

| 1.2. | Comparison of approaches                                           | 9  |

| 2.1. | Model checkers and translation tools input languages               | 19 |

| 4.1. | PROMELA basic types                                                | 34 |

| 4.2. | Numeric Types conversion rules                                     | 35 |

| 4.3. | Correspondence between Ada predefined types and PROMELA types      | 35 |

| 4.4. | The translation of the Ada predefined boolean type to PROMELA      | 36 |

| 4.5. | Operators precedence level                                         | 57 |

| 4.6. | Operators precedence order                                         | 58 |

| 5.1. | Pattern property annotations                                       | 74 |

| 6.1. | Result analysis of Readers-Writers                                 | 84 |

| 6.2. | Result analysis of Separation Kernel                               | 93 |

| 6.3. | Result analysis of Separation Kernel with a protected object       | 94 |

# Listings

| 5.1. | Incorrect model due the absence of end label                                                                                                                                 | 7   |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.2. | Correct model using end label                                                                                                                                                | 7   |

| 5.3. | Incorrect model due the absence of progress label                                                                                                                            | '8  |

| 5.4. | Correct model using progress label                                                                                                                                           | 78  |

| 5.5. | Incorrect model using accept label                                                                                                                                           | 78  |

| 5.6. | Correct model using accept label                                                                                                                                             | '8  |

| 6.1. | The protected object RW                                                                                                                                                      | ; ] |

| 6.2. | The body of task Reader                                                                                                                                                      | ) 2 |

| 6.3. | The body of task Writer                                                                                                                                                      | ) 2 |

| 6.4. | Route operation                                                                                                                                                              | 12  |

| 6.5. | The principal MMR system operations                                                                                                                                          | :   |

| 6.6. | Route operation - original code                                                                                                                                              | 14  |

| 6.7. | Route operation - error code                                                                                                                                                 | 14  |

| 6.8. | Route operation - first iteration                                                                                                                                            | ٥   |

| 6.9. | Route operation - second iteration                                                                                                                                           | 16  |

| A.1. | The Ada program of Producers-Consumers                                                                                                                                       | ) 8 |

| A.2. | The extracted model from the Producers-Consumers program $\dots \dots \dots$ | Į   |

| B.1. | The specification of package $Lbl\_t$                                                                                                                                        | ŀ   |

| B.2. | The specification of package $Msg_t$                                                                                                                                         | ŀ   |

| B.3. | The body of package $Msg_t$                                                                                                                                                  | .(  |

| B.4. | The specification of package $Mem\_t$                                                                                                                                        | . 7 |

| B.5. | The body of package $Mem_t$                                                                                                                                                  | . 7 |

| B.6. | The specification of package <i>Memory</i>                                                                                                                                   | . 7 |

| B.7. | The body of package <i>Memory</i>                                                                                                                                            | 8   |

| B.8. | The specification of package <i>Policy</i>                                                                                                                                   | 8   |

| B.9. | The body of package <i>Policy</i>                                                                                                                                            | 8   |

| B.10 | . The specification of package $Mmr$                                                                                                                                         | Ć   |

| B.11 | .The body of package $Mmr$                                                                                                                                                   | !(  |

| B.12 | The system main program                                                                                                                                                      | ٠.  |

| B.13. Package $Lbl\_t$ translation         | 124 |

|--------------------------------------------|-----|

| B.14.Package $\mathit{Msg\_t}$ translation | 124 |

| B.15.Package $Mem\_t$ translation          | 126 |

| B.16.Package Memory translation            | 126 |

| B.17. Package $Mmr$ translation            | 128 |

| R 18 The main translation                  | 136 |

# 1. Introduction

The work presented in this document was developed in the context of the EVOLVE project, a project that in Portugal was promoted jointly between Critical Software SA and the University of Minho, and intended to propose techniques and tools capable of verifying and validating software products along all of the development phases. The target domain are the so-called reactive systems, i.e., systems that react to environment stimuli. The verification of these systems intends to focus particularly on concurrency aspects, due to the difficulty of stating the correctness of concurrent systems. Most embedded systems, commonly used in many critical missions, belong to the class of concurrent reactive systems.

In particular, this work intends to address the formal verification of critical systems at the implementation level. More specifically, we fous on the analysis of the source code of concurrent systems through the use of formal methods techniques. Formal methods have been used in different phases of the software development process, in particular at the system specification level, which can be considered already a mature topic. However, their usage in source code verification has only recently been addressed.

The present work describes a formal tool called Ada Translation to Spin (ATOS). The tool supports the verification of Ada programs using the model checking technique. More precisely, this work focuses on verifying the source code of concurrent programs written in Ada [TDB+07, BA09], although it can also be useful for verifying sequential Ada programs.

The remainder of this chapter contains an introduction to several essential topics, aiming to frame this work in the formal verification context.

# 1.1. Formal Verification of Software Systems

Information systems have nowadays an extremely high importance in our lives, whether as an essential support for highly efficient communication systems, or in the support of systems essential for the evolution of medical and avionics sciences. The rapid growth of these systems, prompted by the evolution of several different economic sectors, have quickly led to the increase of the complexity of the computer programs underlying these systems. Currently, most software systems are characterized by such a high level of complexity that it is now more difficult than ever to have a reasonable degree of confidence in their reliability.

Attaining absolute certainty that a software system has no errors, i.e. ensuring that it will not produce any unexpected behavior, is clearly an utopia. However, increasing the degree

of confidence in software systems is a central and justified concern, since errors (the so-called bugs) have consequences. The cost of a system failure is not the same in all systems; in *high* integrity systems or critical systems failures may be catastrophic.

On the fourth of July 1996, less that a minute after lunching, the rocket Ariane 5 was destroyed by its automated self-destruct system. After the accident inspection carried out by European Spatial Agency (ESA) and Centre National d'Etudes Spatiales (CNES), a report was produced explaining the reasons for this accident. The report revealed that the destruction of Ariane 5 was caused by an error in software design: the conversion of a 64-bit floating point number to a signed 16-bit integer was at the origin of the accident. In this accident no lives were lost, but the damages approached 260 million Euros.

Presently, in the majority of software systems deployed the certification is made essentially through the *testing* mechanism. This technique consists in passing a set of inputs to the system and observing if the obtained outputs correspond to the ones expected. In the attempt to increasing the efficiency of the input set, which leads to a higher certification degree, a huge broad of techniques have emerged, and more will certainly appear as a result of the big investments made in this research field. As an alternative to testing we find *formal methods*, which encompass techniques capable of providing high levels of assurance. Due to the high costs associated with their usage, formal methods have mainly been used in the development of critical software systems.

Formal methods Many different definitions of Formal Methods are given in different books and scientific documents. As an example, Formal Methods can be seen as "the applied mathematics for modeling and analyzing Information and Communication Technology systems" [BK08]. With the growth of systems' complexity and size the interest in formal methods has risen, since they provide a basis for the precise definition of consistency, completeness, specification, implementation and correctness of systems. Formal methods encompass several validation methods such as: deductive verification [Hoa69, Flo67], model checking [JGP99, BK08] or theorem proving [BM83].

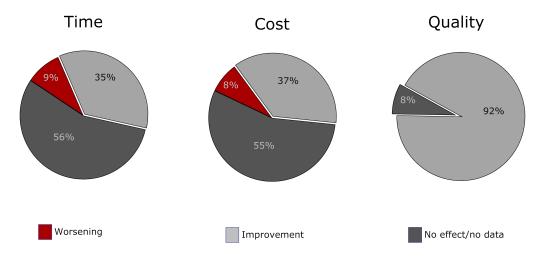

Even though formal methods are seen as very promising in systems' validation, they are currently still seen as very costly and not suitable for the majority of systems. In fact, it is possible to conclude that formal methods are essentially used in the development of *critical systems*, where failures are seen as unacceptable. This vision is explained essentially by the cost-effectiveness relation, and by the difficulty of scaling up the use of formal methods for "big" projects. Nevertheless, a study in [WLBF09] has revealed that the effect of formal methods in several projects, considering time, cost and quality, were very positive as can be observed in Figure 1.1. This study was based on data collected from more than sixty projects (probably, most of them related to critical systems).

Figure 1.1.: Formal methods effect on projects: time, cost and quality

Even so, the time and cost of applying Formal Methods can be reduced through the use of automated techniques (e.g. model checking) and the development of new tools capable of reducing the time and knowledge required for their application. Formal methods techniques will only be suitable for the majority of software deployments when they are capable of providing answers in minutes rather than days.

## 1.2. Verification of Critical Systems in the Industrial Context

The software for critical systems is required to be certified with a high level of reliability, due to the cost associated with failures. Therefore, the industry responsibly for the development of these systems has been progressively increasing its interest in Formal Methods. However, this increasing interest is not simply explained by the potential profits of their application; another reason, probably with more impact, is the explicit recommendation of the application of formal methods in most critical systems standards.

The deployment of safety critical systems is regulated by several standards. These standards vary according to the domain they apply to (medical, defense, railway, aerospace, etc.), but have significant commonalities. In general, they define different assurance levels and different activities/objectives for achieving compliance with each level. For each assurance level, the different activities/objectives are classified as mandatory (M), not required ( - ), or an intermediate value, such as recommendable (R) or highly recommendable (HR), as illustrated in Table 1.1. Typically, formal methods are considered highly recommendable for obtaining the highest assurance levels. More details about the particular safety standards of different industrial sectors are given next.

| Safety Level<br>Requirement | Lowest Level | <br>Highest level |

|-----------------------------|--------------|-------------------|

| 1                           | R            | <br>M             |

|                             |              | <br>              |

| N                           | -            | <br>HR            |

Table 1.1.: The standards generic table to assign the safety level of a system

Avionics Industry The standard DO-178B: Software Considerations in Airborne Systems and Equipment Certification has an important role in the certification of aerospace and defense-related systems. This standard defines five levels of certification known as Design Assurance Level (DAL), which go from DAL E to DAL A, where the Lowest/highest level is DAL E/A. Other standards have originated from DO-178B, like the ESA-Galileo Software Standard (GSW). The application of formal methods in avionics is about to be clarified in a new version of the standard, DO-178C, which shall contain a segment specifically dedicated to the subject.

Railway & Automotive Industry In this industry the standards EN 50128:Railway Applications - Communications, Signaling, and Processing systems stand out. This standard is part of a group of related standards containing the EN 50126 and EN 50129 defined by CENELEC, the European Committee for Electrotechnical Standardization. The EN 50128 specifies five levels of safety, denominated as Safety Integrity Levels (SIL) where SIL0 and SIL4 are the lowest and the highest levels, respectively. The use of formal methods is highly recommend for the highest assurance levels.

Automotive Industry The International Organization for Standardization (ISO) 26262, which was adapted from the International Electrotechnical Commission (IEC) 61508, is a functional safety standard that classifies the system functions in four Automotive Safety Integrity Levels (ASIL), which vary from ASIL-A to ASIL-D, where ASIL-A is the lowest safety-critical level. Formal methods are highly-recommended for ASIL-C and ASIL-D.

Medicine Industry The standard IEC 62304 has an important role in medicine industry, concerning the certification of software for medical devices. The manufacturer classifies software system as whole in three classes: A (No injury or damage to health is possible); B (Non serious injury is possible) and C (Death or serious injury is possible). Based on this classification, IEC 62304 imposes the accomplishment of several requirements along the software development life cycle.

**Common Criteria** The Common Criteria (CC), or IEC 15408, is one of the most commonly used international standards. Unlike the previously presented standards, CC is more oriented

to security-critical, rather than safety-critical, systems. CC evaluates its target systems in seven Evaluation Assurance Level (EAL) ranging between the lowest level EAL1, and the highest level EAL7. The use of formal methods is mandatory for the highest assurance levels.

Formal Methods Tools in Standards Depending on the application and domain, a tool to be used in the certification of a system may have to be itself qualified, prior to its acceptance and usage. As such, a tool based on formal technologies may require self qualification, not necessarily using another formal methods-based tool (otherwise one would enter a vicious cycle). This process is also regulated in the different domains. Acceptable arguments for the qualification of tools are, for example, evidence of a rigorous development process (detailed documentation of the development and verification activities), and "proven in use" evidence, i.e. a track record illustrating that the tool has been successfully applied in several projects.

#### 1.3. Formal Verification of Ada Programs

The Ada programming language was developed at the request of the United States Department of Defense, with the aim of using it as the universal programming language for its military systems. However, the programming language that was originally targeted for military systems quickly proliferated to critical systems in general. Henceforth, the use of Ada in the development of critical systems has progressively increased and remains extremely significant at the present, which is mainly explained by its careful and safe design (as explained in [Bar08]), and the existence of clear guidelines for building this kind of system.

The first standard of the Ada language was published in 1983, and therefore denominated as Ada 83 (but before this date the language proposal had already been published for scientific review). The next version of Ada appeared in 1995, bringing many extension and modifications with respect to the previous version. This new version was denominated Ada 95. The last version of Ada and the one used in the context of this thesis is Ada 2005. This version no longer has the participation of the United States Department of Defense, whose collaboration in this project ceased in 1998. The promotion of Ada is now undertaken by a group of commercial companies, while its standardization had continued under the ISO procedures. A new version of Ada is expected in 2012, which is expected to continue providing new mechanisms for the improvement of systems reliability.

**SPARK** The programming language SPARK [Bar03] is a restricted subset of the Ada language, with added annotations for the specification of the desired behavior of programs, resembling the principles of Design by Contract (DbC) [Mey92]. These annotations are embedded in programs as comments, thereby enabling SPARK and Ada programs to share the same compiler. In other words, a valid SPARK program is also a valid Ada program. SPARK

additionally provides a toolset containing different types of tools for different purposes, such as a static analyzer or an automated theorem prover.

RavenSPARK RavenSPARK [SPA08] is an extension of SPARK compliant with the Ravenscar profile [BDV04, AD03], which aims to make possible the formal verification of concurrent and real-time Ada programs. The restrictions imposed by the Ravenscar profile are the key to make formal verification of concurrent and real-time Ada programs treatable; without these it would be difficult to perform this type of analysis, due to the high level of some Ada features. Beyond the extension of the SPARK subset, RavenSPARK also includes new annotations concerning the additional primitives added to SPARK.

Formal Verification of Concurrent Ada Programs As mentioned, Ada is a programming language endowed with mechanisms that make it very appealing for the development of safe and secure systems. Arguably, the SPARK programming language along with its toolset are the most important landmark of formal verification in Ada programs. RavenSPARK was introduced in an attempt to extend formal verification to concurrent Ada programs, but it is still very limited. There exist of course other approaches to the verification of concurrent programs written in Ada, more precisely through the modeling of Ada programs [HM03, EKPPR03b], but there is still a gap that needs to be filled.

## 1.4. Verification of Software Systems using Model Checking

Model Checking is a formal verification technique suitable for assessing the functional properties of systems. Model checking-based methods are among the most successful formal methods, at least in the industrial context. This is due to their automated nature, which can contribute to significantly reducing the cost of applying the methods, by decreasing the expertise and the time that are commonly required.

Given a model and a property, this technique explores in a brute force manner the states of the model, in order to prove its correctness against the desired property. When a property is not valid for a given model, an error trace is produced containing the path in the model that violates the property. The process of model checking consists in three main phases [JGP99]: Modeling, Specification and Verification. Different approaches to the model checking process are proposed by different methodologies [BK08].

Modeling is the first phase of the process; it consists in converting a design into a formalism, i.e. in translating system requirements into a mathematical model, typically a transition system. Constructing a model that represents exactly the behavior of a system is essential for the success of model checking. It is usually said that "the model checking technique is as good as the model of the system" [BK08].

After the construction of the model, it is necessary to state which properties the model enjoys (or is supposed to enjoy). The *specification* of properties is usually given in some temporal logic formalism, with Computation Tree Logic (CTL) [HR04] and Linear Temporal Logic (LTL) [HR04, Pnu77] having a predominant role. This kind of logic allows for the specification of ordered events, without explicitly using time.

Lastly, the *verification* phase is an automatic process, which checks a property against a model. When the property check fails, i.e. an error is encountered, a trace showing the error path is provided. When error traces are caused by errors or limitations of the models or of the specified properties (rather than of the modeled systems or of the intended properties), they are called false negatives. Even though the verification process is automatic, most often human assistance is needed to overcome some obstacles, such as the state space explosion. Many options are offered to this effect by model checking tools. Choosing the best option is not an easy task and requires some expertise from the user.

The application of the model checking technique to software systems is seen as very promising and has led to the creation of a new research area, known as *software model checking* [DKW08, JM09]. This technique is not simply the application of model checking to software; it involves also the design of solutions to some obstacles in its application, most notably:

Model construction: The manual construction of a model of a software system is an errorprone and time consuming process, due to the complexity of these systems. In addition, there is a gap between the semantics of programming languages for software systems (e.g. C, Ada, or Java) and the input languages of model checking tools. Programming languages have richer features with more complex semantics than modeling languages.

**State explosion:** This is recognizably the biggest problem of model checking. In software model checking the problem can become even more serious, due to the size of software systems, which leads to the generation of models with an enormous number of states. Thus, more aggressive abstractions must be considered.

Property specification: Typically, properties are specified in some variant of temporal logic. This creates two difficulties: firstly, it requires some level of expertise for expressing the desired system properties in temporal logic. Second, the mapping of these properties to the properties of the model may not be straightforward, since the typical specification languages are designed to state properties of mathematical models rather than of source code.

Output interpretation: When a property does not hold in a given model, the model checker reports a counter-example illustrating a trace that evidences the violation of the property. Large models can produce very long traces. As such, manually matching the provided trace to the model's source code can be a really hard task.

#### 1.5. A Formal Approach to the Verification of Ada Programs

The approach presented in this section corresponds to the one embedded in ATOS. The main role of ATOS is to help overcoming some of the software model checking problems (as outlined above), in the application of the model checking technique to Ada programs. In particular, ATOS directly addresses two of these problems: given an Ada program, it is capable of automatically extracting a model from it, overcoming the difficulties expressed in the *model construction* problem, and by inferring properties directly from Ada programs or from annotations embedded in the programs, it tackles also the *property specification* problem.

ATOS uses the Simple PROMELA Interpreter (SPIN) model checker [Hol03] as back-end to perform the verification of the extracted models. SPIN is a model checking tool focused on verifying the correctness of models of concurrent systems, which clearly matches our intents. The models are described in PROMELA, the SPIN modeling language, and correctness claims can be stated through LTL formulas or PROMELA assertions. In short, ATOS generates PROMELA models from Ada programs, and LTL formulas or assertions from inferred and annotated properties.

The ATOS approach and related decisions Software model checking tools follow essentially two main approaches: (i) they either generate input models for one or more different existing model checkers, where ATOS is included, or (ii) they include their own model checking algorithms to check the correctness of the models. Selecting one of these two approaches was not straightforward and required the analysis of the pros and cons of each approach, as enumerated in Table 1.2.

| Approach | Advantages                                                                                                                                                                                                                                                               | Disadvantages                                                                                                                                                                                                                                                                                            |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (i)      | <ul> <li>Less time required;</li> <li>Profit from all the techniques already implemented in the target tool, from abstraction techniques to model checking algorithms;</li> <li>Use a stable and recognized tool (of course it depends from the chosen tool).</li> </ul> | <ul> <li>Little room for development of new techniques related with model checking theories, such as abstraction techniques, or the definition of new mathematical models which can provide less complex and faster algorithms;</li> <li>Restricted to the temporal logic of the chosen tool;</li> </ul> |

| (ii)     | • Opportunity to developed new techniques and theories according to what is intended;                                                                                                                                                                                    | <ul> <li>Significant time and effort required;</li> <li>One could being "reinventing the wheel";</li> </ul>                                                                                                                                                                                              |

Table 1.2.: Comparison of approaches

An analysis of the advantages and disadvantages of approaches (i) and (ii) revealed that both could be equally interesting to explore, but due to the time restrictions of this work, the approach (i) was judged to be more suitable, because it could guarantee results in the short term.

Another important decision in the definition of the ATOS approach was whether or not to use an intermediate representation between the programs and the models. On one hand, using such a representation would give us the possibility to then generate more easily models that could be exported to others model checkers, because the intermediate representation would be closest to a model than the programs. On the other hand, program details might be lost in this intermediate representation, and it was our intention to generate models that would be as accurate as possible. The decision of performing the extraction of models directly to PROMELA without any intermediate representation was due essentially to this fact. It also seemed that it might be relatively easy to generate input models for others model checkers directly from PROMELA, since it provides high-level mechanisms for the specification of models.

#### 1.6. Contributions and Document Outline

Our most important contributions in this work are are:

- a model extraction mechanism, which automatically generates PROMELA models from Ada programs;

- 2. several mechanisms supporting the extraction of properties from annotated Ada programs to PROMELA models; and

- 3. as a case study of significant size to help validate our approach, the verification of a Separation Kernel subsystem using these mechanisms.

- 4. The background material contained within this thesis, which surveys themes like model checking, software model checking and the Ada programming language.

A paper containing part of this work was presented at the *Embedded and Real-Time Systems* track of <u>INForum 2011</u>. A new paper containing all of ATOS' features including the new supported Ada primitives and the new case study (the Separation Kernel) is about to be prepared.

The rest of this document is organized as follows. First, some background information about software model checking is given in Chapter 2, concerning its different approaches, theories and tools. Chapter 3 introduces ATOS, and chapters 4 and 5 explain the model and property extraction mechanisms implemented in it, respectively. Then the application of ATOS is demonstrated in Chapter 6 through two case-studies: *Readers-Writers* and *Separation Kernel*. Lastly, a discussion of the developed work along with its limitations and future improvements is given in Chapter 7.

# 2. Model Checking - Approaches, Theories and Tools

A broad range of model checking tools are available. Even though these tools follow all the same technique, the approaches and theories implemented in each are very different. The application of the model checking technique, whether on software or hardware systems, requires some knowledge of these concepts. Therefore, in the context of this work, a deep study was performed with the aim of obtaining the sufficient knowhow for the development of a tool like ATOS.

Our research of model checking techniques began with the study of the different mathematical model theories, in order to understand their semantics and decide whether there were one most suitable for our intents. Along with the mathematical models, several different approaches to the logical formalism used in model checking (*Temporal Logic*) were studied. This formalism enables the specification of properties required for correctness of the models.

The next step of research was the study of model checking tools, realizing what approaches and theories were followed by each, and analyzing its application in systems verification. Despite software model checking having only recently emerged as a research field, there exist already several (software) model checkers targeted to support the verification of software systems. Therefore, a study of some software model checking tools was also carried out, with particular focus on the ones that support the verification of Ada programs.

The research described above was very important in the definition of the ATOS approach. Many questions such as whether to Use or not an existing model checker, or the choice of the most adequate model checker to use as ATOS back-end, were answered based on all the information collected along this research process. The research was also important to realize how we may contribute to the verification of Ada programs using the model checking technique.

In the remaining of this chapter an overview of mathematical models is first presented, along with details about the two main theories: Petri Nets and Automata. Next, an introduction to temporal logic is given, covering the details of some different temporal logic approaches. Lastly, several model checking and software model checking tools are analyzed.

#### 2.1. Mathematical models

A formal model is an essential piece in the model checking technique puzzle, because it allows the representation and reasoning about the system behavior. Formal models have a mathematically defined syntax and semantics. Such models can be manipulated by a computer tool and can be used to verify system properties, i.e., to prove that certain desired properties are fulfilled, or that certain undesired properties are guaranteed to be avoided.

Our purpose here is to identify and analyze the characteristics of mathematical models, in order to understand which is the "ideal" model to represent a concurrent software system. Next, it will be analyzed two of the most used mathematical models in model checking: Automata and Petri Nets.

#### 2.1.1. Automata

Automata models are transition systems, where nodes represent the state of a system in a given moment and the edges (transitions) specify how the system evolve. A Deterministic Finite Automata (DFA) is a 5-tuple (S, s0, L, F, T), where S is a finite set of states, s0 is the initial state, L is the set of labels (the actions executed in transitions),  $F \subseteq S$  is the set of final states and  $T \subseteq S \times L \times S$  is the transition relation.

A path<sup>1</sup> in the model is an ordered sequence of labels. In DFA paths are finite, which makes impossible the representation of non-terminating systems. This restriction can be solved with a simple method called Buchi-acceptance [Per90], where infinite runs are enabled. DFA's have another constraint, they can not represent non-deterministic actions contained in systems behavior. Transforming a DFA into a non-deterministic Automata (NFA) is a simple process [HMU06], in fact these two structures are equivalent, i.e, each DFA can be converted into a NFA and vice-versa. Finally, to represent concurrent systems it is only missing the simulation of concurrency, which can be achieved by the product of NFA's (i.e the joint of two NFA's).

The use of Automata models in model checking, is a stable matter. Many successful model checkers use Automata models as a basis for theirs transition system definition (e.g. SPIN uses NFA's as mathematical model).

#### 2.1.2 Petri Nets

Petri Nets [PR08, DJE01] as graphical and mathematical model, provide a uniform environment for modeling concurrent systems. The transition system of Petri Nets are composed by nodes and arcs. There are two types of nodes: places and transitions, which are connected by arcs. Arcs only connect places and transitions or vice versa, they do not connect two places or two transitions. The hold of conditions is represented by tokens in places. Transitions are only activated if and only if there is at least one token at each of its input places.

<sup>&</sup>lt;sup>1</sup>Paths are also named as runs

The representation of systems is usually done by high level Petri Nets like Colored Petri Nets (CPN) [Jen95]. CPN's combine the capabilities of Petri Nets (control structures, synchronization, communication and resource sharing) with the capabilities of a high programming language (data and data manipulations).

Every Petri Net can be converted into a CPN and vice versa, so there is no theoretical difference between them. However CPN is a much more compact and convenient modeling language than Petri Net. CPN's are to Petri Nets as high level programming languages are to assembly.

A bunch of verifications methods exist to provide Petri Nets analysis. Model checking algorithms are included in these methods. There are already some model checking tools using Petri Nets as mathematical model (e.g. Quasar).

### 2.2. Temporal Logic

The temporal logic allows the specification of properties over a given period of time. The time may be implicit or explicit, and enables the specification of an ordered sequence of events. The model checking technique is based on temporal logic, thereby enabling the specification of formulas (properties) which validate a set of model states rather than single points as it proposed by the traditional propositional or predicate logic. Therefore, in the context of software model checking, temporal logic is very useful and can really simplify the specification of properties due to its capability to state properties for regions of code rather than single points in implementation.

Several temporal logic approaches have been proposed until now, each with a different purpose. These different approaches may be distinguished by theirs *view of time*. Next, are presented two of this views denominated as LTL and CTL. These may be considered the most important ones, since are the basis for many others, such as CTL\* and TCTL, also presented in this section.

#### 2.2.1. LTL

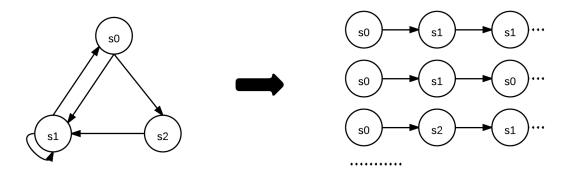

The Linear Temporal Logic (LTL) views time as a set of individual paths, where a path is a sequence of events (states). An example of how LTL views a given transition system is illustrated in of Figure 2.1. LTL contains several connectives which encompass the "normal" operators (common to the traditional logic formalisms) such as:  $\land$ ,  $\lor$ ,  $\rightarrow$ ,  $\leftrightarrow$ , but it also encompasses other connectives<sup>2</sup>. These connectives allow the reference of (implicit) time in models such as: F (in a future state), G (all future states), X (next state) and the binary operators U (Until) and W (Weak-Until). Where the formula  $\phi$  U  $\psi$  holds on a path if  $\phi$

<sup>&</sup>lt;sup>2</sup>There exist several different terminologies to represent the same connectives we depict one of these

holds on all states path  $until\ \psi$  holds and  $\psi$  must hold at some future state. The  $\phi\ W\ \psi$  is similar to the previous however it is not required that  $\psi$  holds in some state.

Figure 2.1.: The LTL view of time

#### 2.2.2. CTL

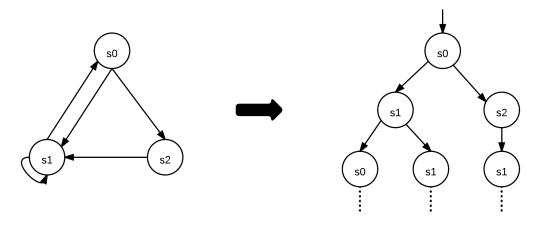

The Computation Tree Logic (CTL) which belongs to the *branching-time logics*, views time as a tree of paths. A similar example to one used in LTL is utilized again (Figure 2.2), but now to illustrate the CTL view of time. The CTL view of time unlike the LTL, allows one to assert the *existence* of a path rather than just state properties over *all* paths.

The CTL has the same time operators as LTL but now they are quantified over the paths. Therefore, the temporal operators appear as pairs: the first part is the quantifier which can be A (all paths) or E (exists at least one path); while the second part may contain the already introduced X, F, G, and U operators (The W did not exist but it is derivable). As an example, the formula EF  $\phi$ , means "exists a path in a future state where  $\phi$  holds".

Figure 2.2.: The CTL view of time

#### 2.2.3. CTL\*

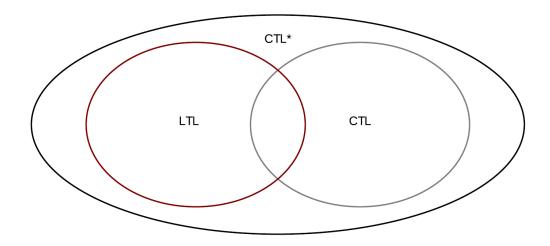

The CTL\* [EC82] is a superset of CTL, that combines the expressive power of LTL and CTL as illustrated in Figure 2.3. As mentioned, LTL does not allow the quantifications over paths permitted in CTL. Nevertheless, CTL does not include all the expressive power of LTL too, since LTL permits the selection of range paths, which is impossible in CTL.

CTL\* combines the expressive power of LTL and CTL by dropping the CTL constraint which requires that all temporal operators (X, F, G, and U) must be preceded by a quantifier (E and A). Thus, CTL\* encompass two classes of formulas: *state formulas* (evaluated at state level) and *path formulas* (evaluated along paths).

Figure 2.3.: CTL\* expressive power

#### 2.2.4. TCTL

The Timed Computation Tree Logic (TCTL) [ACD93, LPY95] is an extension of CTL, allowing the use of explicit time constraints in properties specification. For example, in the property "in all future paths p is valid" expressed as AF p it is possible the addition of a time restriction. Thus, one can state in "all future paths p is valid within 10 units of time" as  $AF_{\leq 10}$  p.

TCTL requires a different transition system comparing to the one used previously (in LTL and CTL). The main difference between them is the addition of *clocks* to the (timed) models. A number of finite clocks defined in  $\mathbb{R}_{\geq 0}$ , may exist in a model, these evolve synchronously as if there was a global clock controlling the entire system, nevertheless, the clocks reset can be performed individually.

#### 2.3. Model Checking - Tools

The first model checkers start to be developed in the early 80's, since then a significant number of model checking tools had appeared. Most of these tools are focused on the verification of concurrent systems, in fact these systems were in the model checking origin, from Edmund Clarke in [Cla08] we quote "Model Checking did not arise in a historical vacuum. There was an important problem that needed to be solved, namely Concurrent Program Verification".

Amongst the model checking tools we highlight three: SPIN; NuSMV; and Uppaal. The SPIN because was one of the first model checkers and it is probably the most successful one; NuSMV for being the first symbolic model checker<sup>3</sup>; and Uppaal for incorporating timed models (timed automata), allowing the use of explicit time, essential in the verification of real-time systems. These three tools were presented in the remaining of this section.

#### 2.3.1. SPIN

Simple PROMELA Interpreter (SPIN) is a general tool for verifying the correctness of distributed software models and belongs to the category of model checker's [Hol03]. It was written by Gerard J. Holzmann and others in the original Unix group of the Computing Sciences Research Center at Bell Labs, beginning in 1980.

Modeling language and property specification SPIN targets efficient software verification and hardware verification. The tool supports a high level language to specify systems descriptions, called Process or Protocol Meta Language (PROMELA). SPIN is essentially used to trace logical design errors in distributed systems by supporting requirements specification in Linear Temporal Logic (LTL) or embedded assertions in models. LTL presented in SPIN has the following syntax:

$$\phi ::= \ true \ | \ false \ | \ 0 \ | \ 1 \ | \ p \ | \ \neg \ \phi \ | \ \phi \ \land \ \phi \ | \ \phi \ \lor \ \phi \ | \ \phi \rightarrow \phi | \ [] \ \phi \ | \ <> \ \phi \ | \ \phi \ U \ \phi$$

where p is propositional atom and the connectives [] (equivalent to G operator), <> (equivalent to F operator) and U are the temporal connectives. As previously explained, these connectives mean: [] all future states; <> some future state and U until the state.

**Verification** There are three main modes for the verification of models in SPIN tool: <u>Simulator</u>, allowing for rapid prototyping with a random, guided, or interactive simulations; <u>Verifier</u>, capable of rigorously validate of user specified correctness requirements (using partial order reduction, collapse compression and minimized automata theories to optimize the search) or

<sup>&</sup>lt;sup>3</sup>The primary version of NuSMV (SMV) was the first symbolic model checker

validate even very large system models with maximal coverage of the state space using abstraction techniques like *hash compact* and *bitstate*. <u>Driver for swarm verification</u> (a new form of swarm computing), which can make optimal use of large numbers of available compute cores to leverage parallelism and search techniques, which may increase the chance of verifying large models by speeding up this process.

#### 2.3.2. Uppaal

Uppsala [BDL04] is a toolbox for the verification of real-time systems jointly developed by Uppsala University and Aalborg University. The tool was designed to verify systems modeled as networks of timed automata extended with integer variables, structured data types, and channel synchronization. In Uppsal, the state of the system is given by the location of all automata, the clocks, and the values of the variables. A timed automaton is a finite-state machine extended with clock variables. It uses a dense-time model, i.e., when a clock variable evaluates all the clocks advance too, in a synchronously manner.

Modeling language and property specification The Uppaal modeling language is a mix between the graphically design of system entities behavior and the specification of data structures and functions described in a C similar language. The query language of Uppaal, used in property specification process is a subset of Timed Computation Tree Logic (TCTL). As mentioned, TCTL among others allows the use of time constraints in the specification of properties.

**Verification** The Uppaal tool has two main modes, one that presents a graphical visualizer for quickly and efficient simulation and another where properties may be specified and then validated. In the latter, different algorithms search (depth-first and breadth-first) and abstraction techniques (allowing different modes for the space state representation and techniques that reduce the state space) were provided.

#### 2.3.3. NuSMV

The New Symbolic Model Verifier (NuSMV) is based on the SMV model checker, actually it is the reimplementation of the latter. The SMV model checker was the first symbolic model checker, and as such was in the origin of this new class of model checking tools [McM93]. The symbolic model checkers aim to tackle the main problem of model checking, the state explosion, by introducing the concept of symbolic representation. This concept allow the manipulation of sets of states rather than single states as in the classic model checking approach, where the symbolic techniques Binary Decision Diagram (BDD) and Satisfiability Solving (SAT) have a prominent role.

Modeling language and property specification The modeling language of NuSMV was inherited from SMV, and it describes finite state machines. The specification of a NuSMV model is made using modules, which have parameters and may be instantiated several times. There must be at least one main module per system (like in C language). The modules specification have a variable declaration part and an assignment part. The assignment part may be divided in two different parts: the variables initialization; and the definition of system transitions, which is made indicating the value (or the values, allowing non-determinism) of variables for the next state. The described systems specification process is very extensive and along with the obligation of array indexes and parameters having to be constants, make the NuSMV modeling language quite low-level. The properties specification is made in the models within the modules declaration. NuSMV supports the specification of formulas in both LTL and CTL formalism (including one predefined pattern of properties, the invariants).

**Verification** The verification of NuSMV models includes both model simulation and validation. In the latter, are offered the classic model checking algorithms (i.e, the exhaustive verification) for BDD's representation and the bounded model checking algorithms using a propositional SAT solver. The bounded model checking algorithms unroll the finite state machines only for a fixed number of steps, thereby reducing the resources required for the verification but also decreasing the effectiveness of verification.

## 2.4. Software Model Checking - Tools

The earlier model checking tools (e.g. SPIN) were not prepared to perform the verification of software systems. Many problems (already enumerated) emerged when it was tried the application of model checking technique to software. In order to solve these problems a new generation of model checkers came up (the software model checking tools). These new tools have among others automated the modeling phase by starting to receive programs as input instead of models. In Table 2.1 are illustrated some of these software model checking tools as well as their supported input programming language. In the rest of this section were analyzed four of these model checking tools: Quasar, Ada Translating Toolset, BLAST and BANDERA.

| Model<br>Checking<br>Tools | Input Language |  |

|----------------------------|----------------|--|

| SPIN                       | PROMELA and C  |  |

| BLAST                      | С              |  |

| Quasar                     | Ada            |  |

| BANDERA                    | Java           |  |

| Ada                        |                |  |

| Translating                | Ada            |  |

| Toolset                    |                |  |

| SLAM                       | С              |  |

| Java Path<br>Finder        | Java           |  |

Table 2.1.: Model checkers and translation tools input languages

#### 2.4.1. Quasar

Quasar [BPP99, EKPPR03a] is a model checker tool, that enables the specification and verification of temporal properties on concurrent Ada programs. Quasar receives Ada programs as input, converting them into high level Petri Nets.

The translation process of an Ada program to a CPN performed in Quasar, can be divided in two phases.

- 1. The whole Ada program is converted into a set of generic Petri Nets, where each Petri Net is an Ada construction. These generic Petri Nets have abstract transitions that are then replaced by the correct sub net, this operation is called substitution.

- 2. The set of produced Petri Nets in (1) is then combined through merging operations. These operations combine two Petri Nets by merging places having the same name.

```

task body Client is

Begin

Loop

server.service

End loop

End Client

task body Server is

Begin

Loop

accept service

End loop

End Client

```

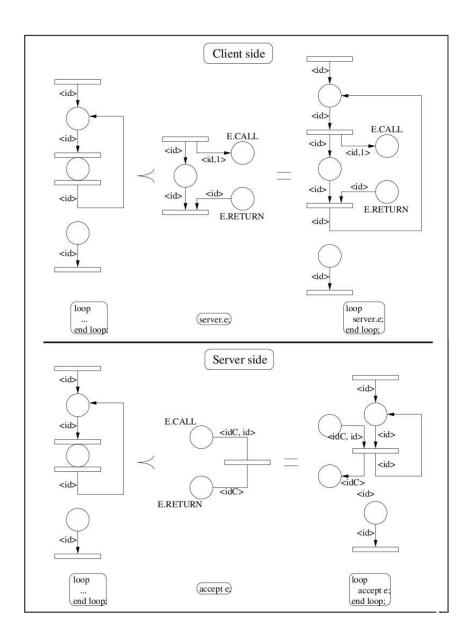

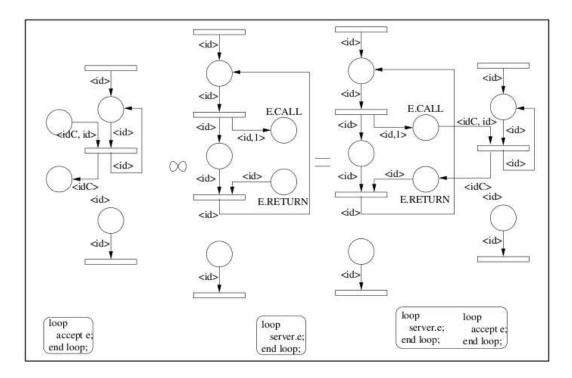

To clarify the translation process performed by Quasar, Figures<sup>4</sup> 2.4 and 2.5 illustrate the first and second phases, respectively, for the translation of the above Ada program (The  $\prec$  and  $\bowtie$  operators present in Figures 2.4 and 2.5, represent the substitution and merging operations, respectively).

Figure 2.4.: The first phase of Quasar translation process

<sup>&</sup>lt;sup>4</sup>Figure imported from [EKPPR03a]

Figure 2.5.: The second phase of Quasar translation process

For the design of temporal properties, Quasar provides four templates: state accessibility, bounded wait, critical section and stable property. These templates are LTL formulas and correspond to the most common properties, for more information about them see [EKPPR03a]. The validation of Quasar extracted models is performed with High Level Net Analyzer (HELENA) [Eva05].

## 2.4.2. BLAST

Berkeley Lazy Abstraction Software Verification Tool (BLAST) [BHJM07] is an automatic verification tool for checking temporal safety properties of C programs. Given a C program and a property, Blast answers the question "Does the program satisfies the property?". If the answer is *no* it provides an execution path that exhibits a violation of the property (or, since the problem is undecidable, does not terminate).

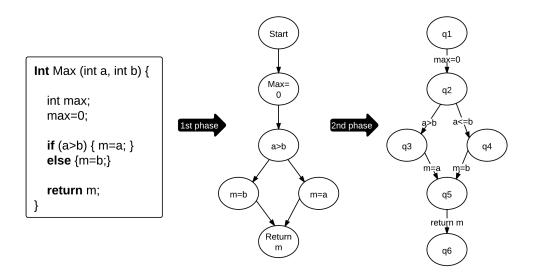

BLAST uses C Intermediate Language (CIL) [NMRW02] to extract information from C programs, this information is crucial in the model extraction process. Programs are internally represented as a set of Control Flow Automata (CFA), one for each function. A CFA is a directed graph, where states correspond to control points of the program and edges correspond to program operations. There exist four types of program operations: blocks of assignments, assume predicates<sup>5</sup>, function calls and return instructions. To translate a program to a set of

<sup>&</sup>lt;sup>5</sup> An assume predicate is the condition that must hold to execute a certain transition

CFA's BLAST use an intermediate representation, which is the Control Flow Graph (CFG) of the correspondent program. Figure 2.6, demonstrates the extraction process of *Max* program performed by Blast. *Max* is a simple program which receives two integers and returns the bigger one.

Figure 2.6.: The translation of program Max done by Blast

The verification on BLAST can be done, through these three forms: reachability checking, assertion checking and temporal safety specifications. Reachability checking is made through the use of labels, the user may annotate labels in C programs enabling BLAST to check whether such labels are reachable or not in the source code. Assertions are checkpoints of programs, where a given property must hold and they can be annotated everywhere in C program. For the specification of temporal properties, BLAST has its own specification language, which is given in terms of program events.

#### 2.4.3. Ada Translating Toolset

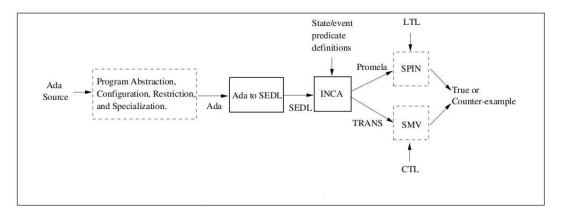

The Ada Translating Toolset [DPC98] converts Ada programs to input languages of different model checkers (SPIN and SMV). Thereby enabling, in an automatic way, the verification of an Ada program by different model checking tools.

Initially this toolset, converts the original Ada program to a safe finite-state variant by applying program abstractions, configuration, restriction and specialization enabling the creation of a tractable model to apply model checking technique. The transformed code is then converted to S-Expression Design Language (SEDL) [Cor93] using the IRIS-Ada toolset. SEDL allows the specification of concurrent systems in a compact language notation that can be easily converted into finite state Automata. The next step is the design of properties in INCA

query language. Finally, with the concurrent system written in SEDL and the properties specified in INCA query language, the INCA tool [Sie02] creates the input model and property for a model checking tool. The described translation process is graphically illustrated in Figure<sup>6</sup> 2.7.

Figure 2.7.: The Ada Translating Toolset approach

#### 2.4.4. Bandera

The Bandera tool is the most complete of the tools presented in this section, because it tackles all of the software model checking main problems. The Bandera project was carried out by an experienced team, involving many people who had participated in the Ada translation Toolset development. However, the Bandera tool whose the first released was set up in 2005 is no longer supported.

Bandera receive Java programs as input and is able to extract from these, input models for several model checkers. The specification of Java programs properties is available through Bandera Specification Language (BSL), an own language based on source-code annotations, with a similar syntax to the already "dead" Java Modeling Language (JML) [BCC+03]. BSL enables the specification of temporal properties through the same high level mechanism of ATOS, which encompasses a set of predefined pattern properties (see Section 5.2.1). Assertion on Java programs were also allowed in BSL, as well as the specification of observable properties (commonly denominated as invariants) of different Java control points.

At first, Bandera converts Java programs into an intermediate representation using Jimple language as support. Jimple is essentially a language of control-flow graphs, targeted to be a Java decompiler. Next, with the intermediate representation and the properties specified in BSL, Bandera builds the Bandera Intermediate Representation (BIR) using a tool named BIR constructor. Lastly, from BIR Bandera is able to generate input models for four different model checkers: SPIN, dSPIN (a no-longer spin extension with functions and pointers) [DIS99], Symbolic Model Verifier (SMV) (the origin tool of New Symbolic Model Verifier (NuSMV)

<sup>&</sup>lt;sup>6</sup>Figure imported from [DPC98]

tool [CCGR00]) and Java Path Finder (JPF) [Hav99] (which was initially a Java translator to SPIN that was then converted into a standalone model checker).

Bandera also encompasses a back-trace mechanism, enabling an easy mapping of the error traces provided by the enumerated model checkers, and two program abstraction techniques: program slicing and abstract interpretation, whose details are presented next.

**Program slicing** Program slicing is one example of an abstraction model technique. Based on a given property, all lines of a program which do not influence the verification of that property are removed. Thereby reducing the size of program and consequently the number of model states. For example, in a property which checks the value of a variable A, all variables in program that do not influence A's value, can be removed.

Abstract interpretation This technique reduces the model via data abstraction. When a property to be checked does not depend on the program's concrete values but instead depend on the properties of those values, some values could be abstracted. For example, a program may use a vector to store information about people (e.g. age, date of married, number of brothers, etc), but if the property to be checked only depends on a particular information such as being married or not, it is possible to abstract the large number of vector states onto a small set: {married}, not married}.

# 3. An Overview of ATOS

The tool presented in this chapter (ATOS) may be classified as a software model checker, a framework which helps in the application of the model checking technique to software systems (both definitions seem correct). The main goal of ATOS is to help in the overcoming of the software model checking problems identified previously, in an attempt to verify concurrent software systems.

ATOS integrates two mechanisms which are very helpful in taming the <u>model construction</u> and the <u>property specification</u> problems. The mechanism used to tackle the model construction problem is the <u>model extraction</u> whereas the property specification problem is tackled using the property extraction mechanism.

The model extraction consists in the automatic generation of models from programs. In particular ATOS receives as input Ada programs (only the main program is required) and outputs PROMELA models. The technical details of the model extraction process are given in chapter 4.

The properties extraction mechanism results from joining two different mechanisms, one that automatically generates properties from programs and another which builds properties from annotations in Ada programs. The annotation language provided is inspired by SPARK. The properties extracted by these mechanisms can either be in the form of LTL formulas or assertions embedded in the extracted models. More details about these mechanisms are given in chapter 5.

The models and properties extracted by ATOS are then verified with the SPIN model checker. Although the SPIN verification step is an automatic process, the user should have some experience with and knowledge of the SPIN model checker. This experience and knowledge are even more important in the presence of the state explosion problem, since SPIN offers several abstraction techniques and different search algorithms. Knowing how to take advantage of these functionalities could be the difference between being able or not to verify a model.